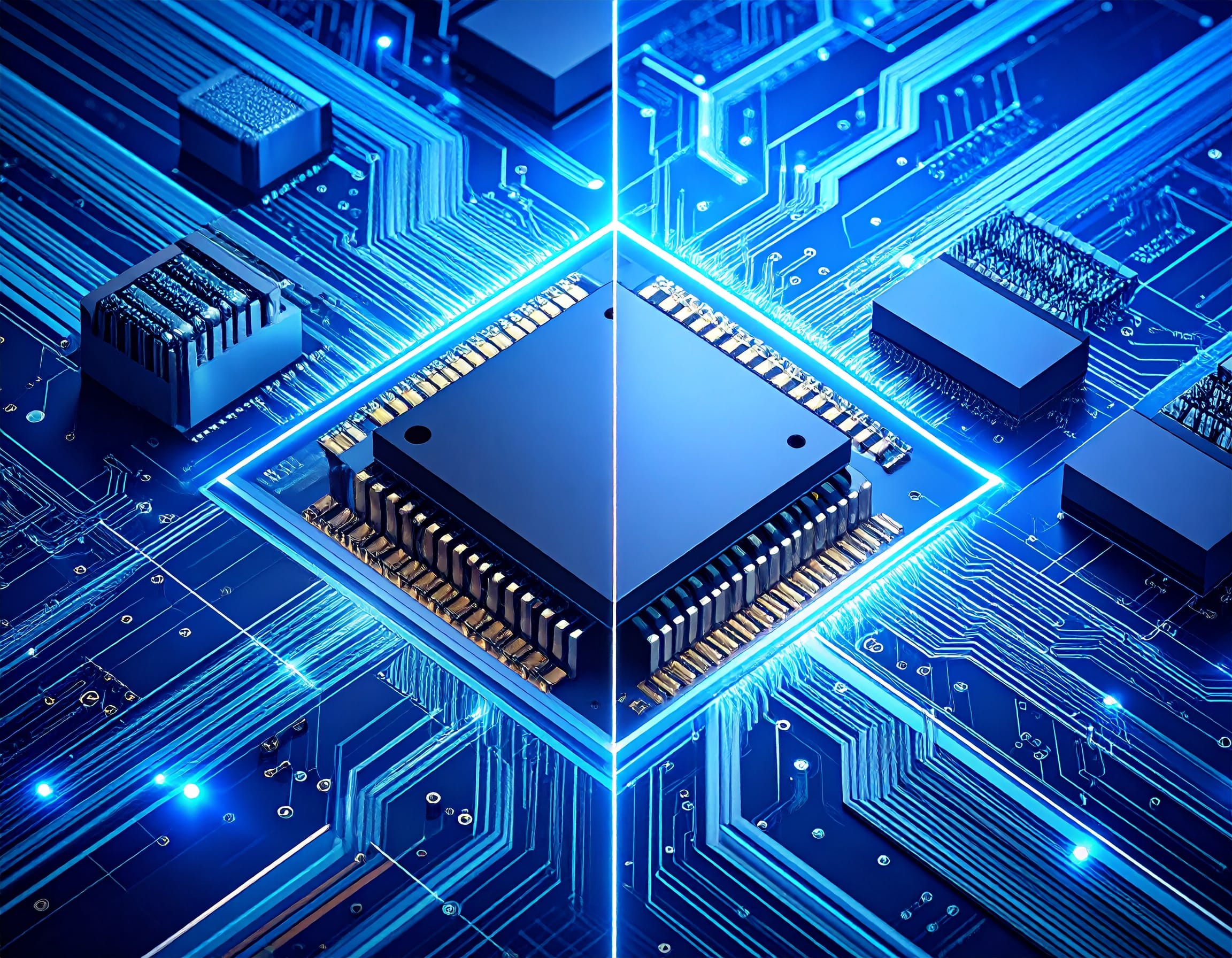

How to Reduce Self-Heating Effect (SHE):

🧱 1. Use Better Thermal Conductive Materials

Replace traditional SiO₂ or low-k dielectrics with materials that have higher thermal conductivity

Example: AlN (Aluminum Nitride) or BN (Boron Nitride) for heat spreading

🌡️ 2. Thermal-Aware Device Design

Wider fins, shorter gate lengths, or multi-fin structures to distribute heat

Increase fin spacing to allow better thermal dissipation

🧯 3. Layout Optimization

Avoid placing high-power devices too close together

Introduce thermal guard bands between hot blocks in analog or digital layout

🧰 4. Use Advanced Cooling Techniques

Add micro heat sinks or embedded thermal vias

Backside cooling (used in 3D ICs) helps remove heat from below the silicon

⚙️ 5. Reduce Power Density

Lower supply voltage (DVFS – Dynamic Voltage and Frequency Scaling)

Use power gating and sleep modes for unused logic blocks

🧠 6. Use Simulation and Modeling Tools

Run thermal simulations during design to predict hot spots

Use electro-thermal co-simulation to evaluate the interaction between power and temperature

💡 Summary Table

| Technique | Effect on Self-Heating |

|---|---|

| High thermal conductivity materials | Improves heat dissipation |

| Wider or spaced fins | Reduces thermal crowding |

| Thermal-aware layout | Spreads hot zones more effectively |

| Advanced packaging/cooling | Removes heat from chip efficiently |

| Low-power design techniques | Reduces heat generation |

📘 Final Thought:

As nodes shrink below 7nm, self-heating becomes a serious reliability and performance issue—especially in analog/RF or high-performance logic. Combining smart design, materials innovation, and thermal-aware layout is essential to minimize SHE.